BENHA UNIVERSITY FACULTY OF ENGINEERING (SHOUBRA) ELECTRONICS AND COMMUNICATIONS ENGINEERING

## ECE 444 Industrial Electronics (2022 - 2023) 1st term

Lecture 5: Digital Signal Conditioning.

Dr. Ahmed Samir https://bu.edu.eg/staff/ahmedsaied

## **Outlines:**

#### Introduction.

Converters.

Comparator.

Digital-to-Analog Converters (DACs).

Analog-to-Digital Converters (ADCs).

#### Introduction

#### 3

#### > Why using digital signal?

- **Reduction of uncertainty.**

- □ Reduction of size, power consumption & failure rate.

- Using computers (in many form) in control enable implementation of:

- ✓ Multivariable control

- ✓ Software linearization of sensor output

- ✓ Solving complicated control equations and modification as needed

- ✓ Using networking for large process complex.

#### Converters

- Most measurements of process variables are performed by devices that translate information about the variable to an analog electrical signal.

- To interface this signal with a computer or digital logic circuit, it is necessary first to perform an analog-to-digital (A/D) conversion.

- Often, the reverse situation occurs, where a digital signal is required to drive an analog device. In this case, a digital-to-analog (D/A) converter is required.

- > The specifics of this conversion must be well known.

Comparator

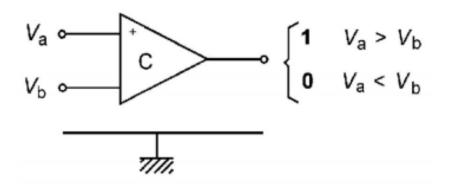

- A basic comparator compares voltages and produces a digital output.

- Simply compares two analog voltages on its input terminals. Depending on which voltage is larger, the output will be a 1 (high) or a 0 (low) digital signal.

- The comparator is extensively used for alarm signals to computers or digital processing systems.

#### Converters

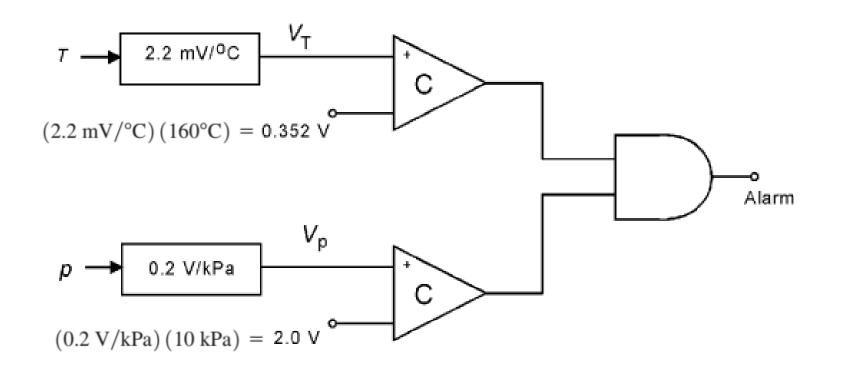

A process-control system specifies that temperature should never exceed 160°C if the pressure also exceeds 10 kPa. Design an alarm system to detect this condition, using temperature and pressure transducers with transfer functions of 2.2 mV/°C and 0.2 V/kPa, respectively.

Solution

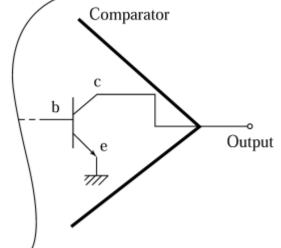

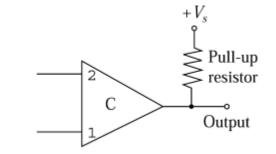

### **Open Collector Output**

Of course, even if there is base-emitter current in the transistor, no voltage will show up on the collector until it is connected to a supply through some collector resistor. In fact, this is exactly what is done when an external resistor is connected from the output to an appropriate power supply. This is called a collector pullup resistor.

- > Advantages to using the open-collector output:

- I. It is possible to use a different power source for the output.

- II. It is possible to OR together several comparators' outputs.

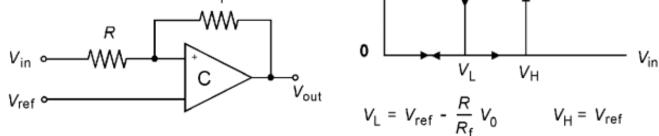

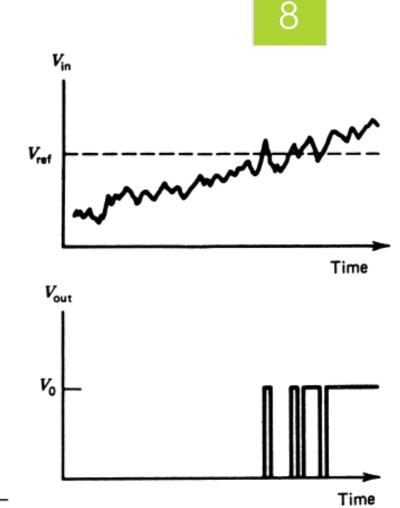

### Hysteresis Comparator

- When using comparators, there is often a problem that the comparator output may "jiggle" back and forth between high and low as the reference level is reached.

- This problem can often be solved by providing a hysteresis window to the reference level around which output changes occur.

- > Once the comparator has been triggered high, the reference level is automatically reduced.  $\frac{R_{f}}{R_{f}}$

#### Converters

EXAMPLE A sensor converts the liquid level in a tank to voltage according to the transfer function (20 mV/cm). A comparator is supposed to go high (5 V) whenever the level becomes 50 cm. Splashing causes the level to fluctuate by ±3 cm. Develop a hysteresis comparator to protect against the effects of splashing.

#### Solution

The nominal reference for the comparator occurs at 50 cm,

$V_{\rm ref} = (20 \,\mathrm{mV/cm})(50 \,\mathrm{cm}) = 1 \,\mathrm{V}$

The splashing, however, causes a "noise" of

$(20 \text{ mV/cm}) \cdot (\pm 3 \text{ cm}) = \pm 60 \text{ mV}.$

This is a total range of **120 mV**. We need a deadband of at least 120 mV, but let us make it **150 mV** for security. Thus, we have

Let:

$$\begin{array}{l} (R/R_f)\,(5\,{\rm V})\,=\,150\,{\rm mV}\\ (R/R_f)\,=\,0.03\\ R_f\,=\,100\,{\rm k}\Omega, \ {\rm then}\ R\,=\,3\,{\rm k}\Omega. \end{array}$$

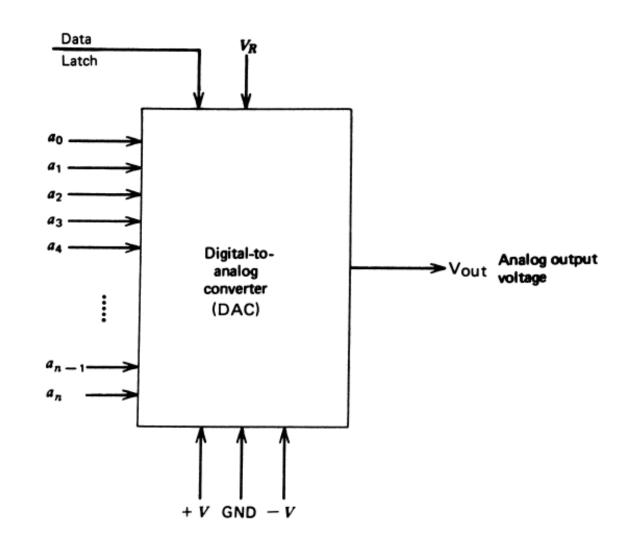

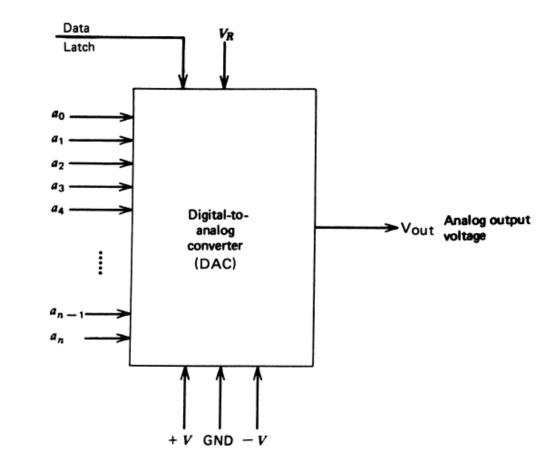

#### Digital-to-Analog Converters (DACs)

- A DAC accepts digital information and transforms it into an analog voltage.

- The digital information is in the form of a binary number with some fixed number of digits.

10

#### A unipolar DAC

11

A unipolar DAC converts a digital word into an analog voltage by scaling the analog output to be zero when all bits are zero and some maximum value when all bits are one.

$$V_{\text{out}} = V_R [b_1 2^{-1} + b_2 2^{-2} + \dots + b_n 2^{-n}]$$

where

$$V_{\text{out}} = \text{analog voltage output}$$

$$V_R = \text{reference voltage}$$

$$b_1 b_2 \dots b_n = n\text{-bit binary word}$$

$$N = \text{base 10 whole-number equivalent of DAC input}$$

- > The minimum output is 0 volt

- > The maximum output depends on the V<sub>R</sub> and n.

- The conversion resolution is the change in analog output for a 1-bit change in binary word  $AV = V 2^{-n}$

$$\Delta V_{\rm out} = V_R 2^{-n}$$

#### A unipolar DAC

**EXAMPLE** What is the output voltage of a 10-bit DAC with a 10.0-V reference if the input is (a) **9**  $0010110101_2 = 0B5H$ , (b) 20FH? What input is needed to get a 6.5-V output?

#### Solution

Let's use Equation (5) for part (a) and Equation (6) for part (b). Thus, for the 0B5H input, we have

$$V_{\text{out}} = 10.0[2^{-3} + 2^{-5} + 2^{-6} + 2^{-8} + 2^{-10}]$$

$$V_{\text{out}} = 10.0[0.1767578]$$

$$V_{\text{out}} = 1.767578 \text{ V}$$

For (**b**), we have  $20FH = 527_{10}$  and  $2^{10} = 1024$ , so

$$V_{\text{out}} = (527/1024)10.0$$

$$V_{\text{out}} = (0.514648)10.0$$

$$V_{\text{out}} = 5.14648 \text{ V}$$

We can use Equation (6) to determine the input needed to get a 6.5-V output by solving for N,

$$N = 2^{n}(V_{out}/V_{R})$$

$$N = 1024(6.5/10)$$

$$N = 665.6$$

The fact that there is a fractional remainder tells us that we cannot get exactly 6.5 V from the converter. The best we can do is get an output for N = 665 = 299 H or 666 = 29 AH. The outputs for these two inputs are 6.494 V and 6.504 V, respectively. The only way to get exactly 6.5 V of output would be to change the value of the reference slightly.

- Some DACs are designed to output a voltage that ranges from plus to minus some maximum when the input binary ranges over the counting states.

- > A simple offset-binary is frequently used.

$$V_{\rm out} = \frac{N}{2^n} V_R - \frac{1}{2} V_R$$

$$V_{\text{out}}(\max) = \frac{(2^n - 1)}{2^n} V_R - \frac{1}{2} V_R = \frac{1}{2} V_R - \frac{V_R}{2^n} \qquad V_{\text{out}}(\min) = -V_R/2$$

#### Bipolar DAC

EXAMPLE A bipolar DAC has 10 bits and a reference of 5 V. What outputs will result from inputs of 04FH and 2A4H? What digital input gives a zero output voltage?

Solution

The inputs of 04FH and 2A4H can easily be converted to base 10 numbers  $79_{10}$  and  $676_{10}$ . Then, from Equation (7), we find

$$V_{\text{out}} = \frac{79}{1024}(5) - \frac{(5)}{2} = -2.1142578 \text{ V}$$

$$V_{\text{out}} = \frac{676}{1024}(5) - \frac{(5)}{2} = 0.80078 \text{ V}$$

The zero occurs when Equation (7) equals zero. Solving for N gives

$$0 = \frac{N}{1024}(5) - \frac{(5)}{2}$$

or  $N = 512_{10} = 200 \text{ H} = 100000000_2$ .

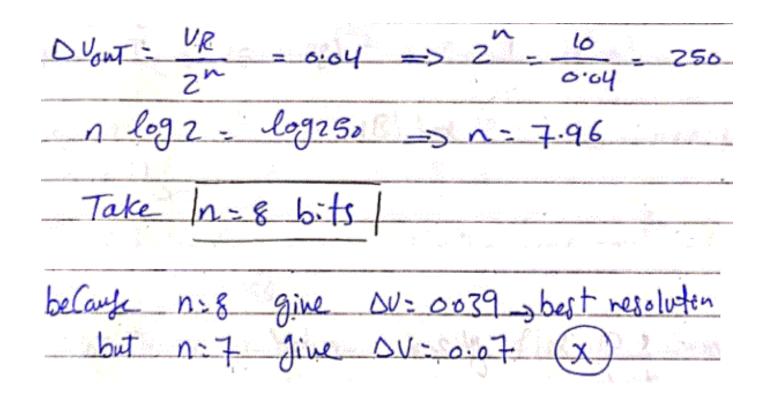

DAC

EXAMPLE Determine how many bits a D/A converter must have to provide output increments of 0.04 V or less. The reference is 10 V.

#### DAC Characteristics

Digital Input (usually TTL logic levels)

Power Supply (single - Bipolar)

Ref. Voltage (internal -external)

Output (unipolar - Bipolar)

Data latch Microprocessor compatible

Conversion time very small (typically msec.)

16

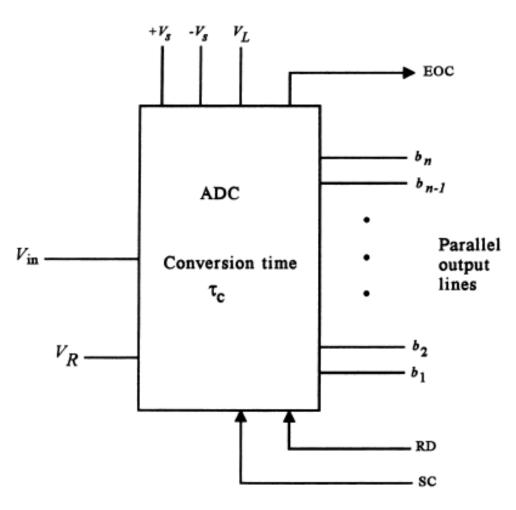

#### Analog-to-Digital Converters (ADCs)

Although there are sensors that provide a direct digital signal output and more are being develop, most still convert the measured variable into an analoged, electrical signal.

With the growing use of digital logic and computers in process control, it is necessary to employ an ADC to provide a digitally encoded signal for the computer.

17

#### A unipolar ADC

The ADC will find a fractional binary number that gives the closest approximation to the fraction formed by the input voltage and reference.

$$b_1 2^{-1} + b_2 2^{-2} + \dots + b_n 2^{-n} \le \frac{V_{\text{in}}}{V_R}$$

The only way the left side can change is if the input fraction changes by only 2<sup>-n</sup> and nothing in between.

> Therefore, there is an inherent uncertainty in the input voltage

$$\Delta V = V_R 2^{-n}$$

> The fractional binary number can be expressed as

$$N = \mathrm{INT}\left(\frac{V_{\mathrm{in}}}{V_R}2^n\right)$$

#### A unipolar ADC

EXAMPLE Temperature is measured by a sensor with an output of 0.02 V/°C. Determine the required

ADC reference and word size to measure 0° to 100°C with 0.1°C resolution.

Solution At the maximum temperature of 100°C, the voltage output is (0.02 V/°C) (100°C) = 2 V

so a 2-V reference is used.

A change of 0.1°C results in a voltage change of

$(0.1^{\circ}C)(0.02 \text{ V/}^{\circ}C) = 2 \text{ mV}$

so we need a word size where

$0.002 \text{ V} = (2) (2^{-y})$

$$y = 9.996 \approx 10$$

#### A unipolar ADC

20

EXAMPLE The input to a 10-bit ADC with a 2.500-V reference is 1.45 V. What is the hex output? Suppose the output was found to be 1B4H. What is the voltage input?

**Solution** We will use Equation (11) to find the solution to these questions. For the first part, we can form the expression

> $N = INT((1.45/2.5)2^{10})$  N = INT(593.92) N = 593N = 251 H

So the output of the ADC is 251H for a 1.45-V input. To get the voltage input for a 1B4Houtput, we solve Equation (11) for the voltage:

$$V_{\rm in} = \frac{N}{2^n} V_R$$

A conversion yields  $1B4H = 436_{10}$ .

$$V_{\rm in} = (436/1024)2.50$$

$V_{\rm in} = 1.06445$  V

However, it is important to realize that any voltage from this to 1.06445 + 2.5/1024 = 1.06689 will give the same output, 1B4H. So the correct answer to the question is that the input voltage lies in the range 1.06445 to 1.06689 V.

#### Bipolar ADC

A bipolar ADC is one that accepts bipolar input voltage for conversion

The most common bipolar ADCs provide an output called offset binary.

$$N = \text{INT}\left[\left(\frac{V_{\text{in}}}{V_R} + \frac{1}{2}\right)2^n\right]$$

$$V_{in} = -V_R/2 \longrightarrow N = 0$$

$$V_{in} = 0 \longrightarrow N = 10000000_2$$

$$V_{in} = \frac{1}{2}V_R - \frac{V_R}{2^n} \longrightarrow N = 1111111_2$$

## ADC Characteristics

- Input must be stable during conversion.

- Power supplies

- Reference voltage (stable well regulated internal/external).

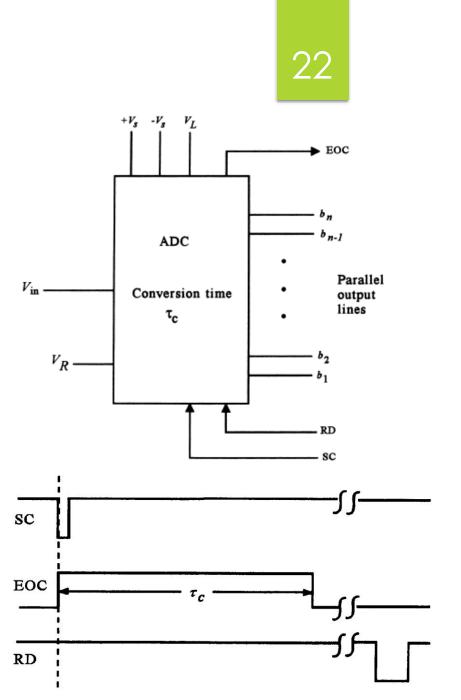

- Control lines (SC- EOC- RD)

- SC (Start-convert): this is a digital input to the ADC that starts the converter on the process of finding the correct digital outputs for the given analog voltage input.

- **EOC** (End-of-convert): When the conversion is complete, the line will go low. This is a digital output from the ADC to receiving equipment.

- RD (Read): The receiving equipment must take the RD line low to enable the tri-states and place the data on the output lines.

Conversion time: The ADC must sequence through a

- process to find the appropriate digital output, and this process takes time.

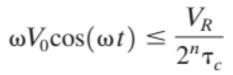

### Conversion Time Consequences

- The finite conversion time of the ADC has serious consequences on the rate of change of signals presented for conversion.

- An ADC performs the conversion process by referring back to the input signal while the conversion is taking place. Obviously, if the input is changing while this process is taking place, errors will occur.

- There is a solution, however. What is needed is simply that the signal not changing during the conversion process.

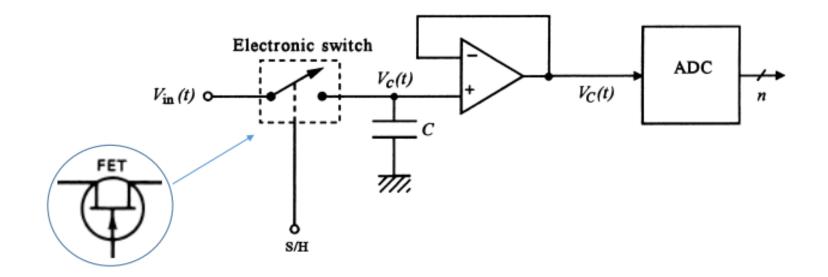

- Therefore, the answer is to hold the value constant during that process. This is accomplished with a sample-and-hold (S/H) circuit.

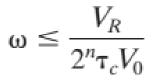

$\frac{dV_{\rm in}}{dt} \le \frac{\Delta V}{\tau_c} = \frac{V_R}{2^n \tau_c}$

$V_{\rm in} = V_0 \sin(\omega t)$

$f \le \frac{V_R}{2^{n+1}\pi\tau_e V_0}$

#### **Conversion Time Consequences**

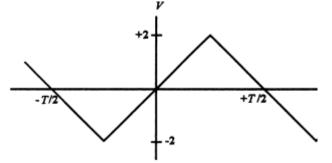

**EXAMPLE** An 8-bit, bipolar ADC with a 5-V reference will be used to take samples of a triangular wave as shown in Figure 19. What is the maximum frequency of the wave if the ADC conversion time is  $12 \ \mu$ s?

#### Solution

The solution is found from the condition expressed by Equation (18). From Figure 19 it is clear that the derivative of the input signal is simply the slope of the triangular wave,

$$\frac{dV_{\rm in}}{dt} = \frac{2}{T/4} = \frac{8}{T} = 8f$$

where T is the period and f is the frequency. Then, from Equation (18),

$$8f \le \frac{5}{2^8(12 \times 10^{-6})} = 1627.6 \,\mathrm{Hz}$$

or  $f \leq 203.5$  Hz.

24

#### Sample-and-Hold

➤ When SC is low S/H electronic switch is opened → the capacitor holds the charge.

> When EOC is low S/H electronic switch is closed  $\rightarrow$  the capacitor charges

The voltage follower (very high input impedance)

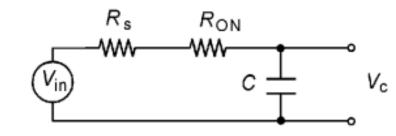

#### Practical Sample-and-Hold

- When S/H electronic switch is closed (Sampling)

- Low-pass limitation:

$$f_c = \frac{1}{2\pi (R_s + R_{\rm ON})C}$$

1

26

- Most commercial S/H circuits reduce this limitation by using a voltage follower before the switch, since it has very low output resistance.

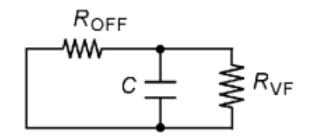

- When S/H electronic switch is opened (Holding)

$$\tau_D = \frac{R_{\text{OFF}} R_{VF}}{R_{\text{OFF}} + R_{VF}} C \qquad \qquad \frac{V_C}{\tau_D} \le \frac{V_R}{2^n \tau_c} \qquad \qquad \tau_D \ge 2^n \tau_c \frac{V_C}{V_R}$$

a) Sampling

b) Holding

#### Practical Sample-and-Hold

27

- **EXAMPLE** A S/H will be used with a 12-bit, unipolar ADC with a 30- $\mu$ s conversion time. The S/H switch ON resistance is 10  $\Omega$ , and its OFF resistance is 10 M $\Omega$ . The voltage follower input resistance is also 10 M $\Omega$ , while the signal source output resistance is 50  $\Omega$ .

- **a.** What value of capacitor should be used?

- b. Determine the sampling cutoff frequency.

Solution

**a.** Equation (24), under the worst-case condition that  $V_C = V_R$  will determine the minimum droop time,  $\tau_D \ge 2^{12}(30 \times 10^{-6}) = 0.12288$  s. Now Equation (22) will allow determination of *C*,

$$\frac{(10^7)(10^7)}{(10^7+10^7)}C \ge 0.12288$$

which gives  $C \ge 0.025 \,\mu\text{F}$ .

**b.** From this result and Equation (22), the critical frequency during sampling is found to be

$$f_c = \frac{1}{(2\pi)(50 + 10)(0.025 \times 10^{-6})} = 108 \text{ kHz}$$

### Sampling Frequency

➤ Acquisition time t<sub>acq</sub> It is the time required for the S/H to reacquire the signal when changing from hold to sample mode. (OFF→ ON)

➤ Aperture time t<sub>ap</sub> It is the time between when a command to hold is given and the actual signal level is held. (ON→ OFF)

➤ Then minimum time between samples is

$$T = \tau_c + \tau_{\rm acq} + \tau_{\rm ap}$$

or max. throughput frequency

$$f_{\rm max} = 1/T.$$

Try this problem:

Mid term 2013: -Felix has become The first skydiver to go faster Than The speed of Sound reaching a max velocity of (1342 km/h) in sumping out of balloon (39 km) above earth, also smashed The record for The highest ever free for - As an electronic engineer, you are asked to design an altitude (height) measurement system for This mission. The require resolution is (10 m) and The altitude sensor used has a T.F (0.1 mv/m) from The block diagram of The suggested system shown, find: (a) Design asuitable s/c ot (b) what is The win number of bits in) of ADC? (c) Tc = 10 msec, are you need S/H Ot or not? prove your answer

29

# END OF LECTURE

# **BEST WISHES**